本文最后更新于2025-04-04,距今已有 380 天,若文章内容或图片链接失效,请留言反馈。

本文为个人的学习笔记,内容均为网络资料总结,价值有限~ 参考资料附在文后

RAM分类

RAM 按照功能可以分为 单端口RAM(SP),简单双端口RAM(SDP),真双端口RAM(TDP)。

按照底层实现可以分为 分布式RAM(DRAM),块RAM(BRAM),寄存器RAM(REG),有些器件也可以用URAM实现(与BRAM类似)。

其中,TDP RAM只能使用BRAM实现,URAM只能实现同步的SDP RAM,DRAM和REG均能实现SP RAM和 SDP RAM。

等位宽SDP RAM

`ifdef RST_ACTIVE_LOW

`define RST_Edge negedge

`define RST_ACTIVE 1'd0

`else

`define RST_Edge posedge

`define RST_ACTIVE 1'd1

`endif

module DCSDP_RAM #(

parameter U_DLY = 1,

parameter RAM_TYPE ="BRAM",// BRAM, DRAM, REG

parameter DATA_WIDTH = 16,

parameter DEPTH = 64,

parameter DEPTH_BIT = 6

) (

input clk,

input [DEPTH_BIT-1:0] wr_addr,

input [DEPTH_BIT-1:0] rd_addr,

input [DATA_WIDTH-1:0] wr_data,

output reg [DATA_WIDTH-1:0] rd_data,

input rd_en,

input wr_en

);

localparam RAM_STYLE = (RAM_TYPE=="DRAM")? "distributed":

(RAM_TYPE=="BRAM")? "block" :

(RAM_TYPE=="REG")? "registers" :

"auto";

(* ram_style=RAM_STYLE *) reg [DATA_WIDTH-1:0] mem[DEPTH_BIT-1:0] ;

always @(posedge clk ) begin

if(wr_en==1'd1) mem[wr_addr] <= #U_DLY wr_data;

if(rd_en==1'd1) rd_data <= #U_DLY mem[rd_addr];

end

endmodule上面这个代码实现了一个简单双端口的RAM,可以选择RAM的类型,设置深度和位宽。

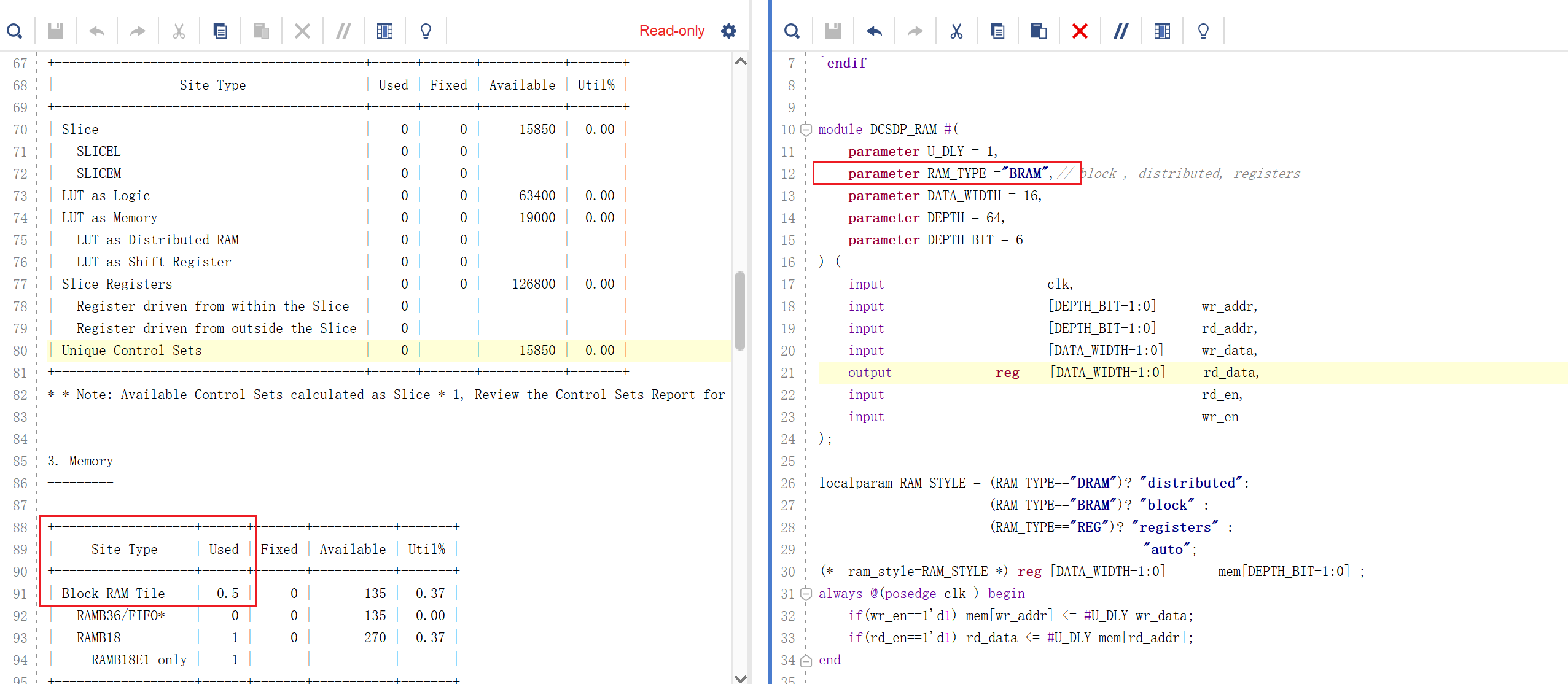

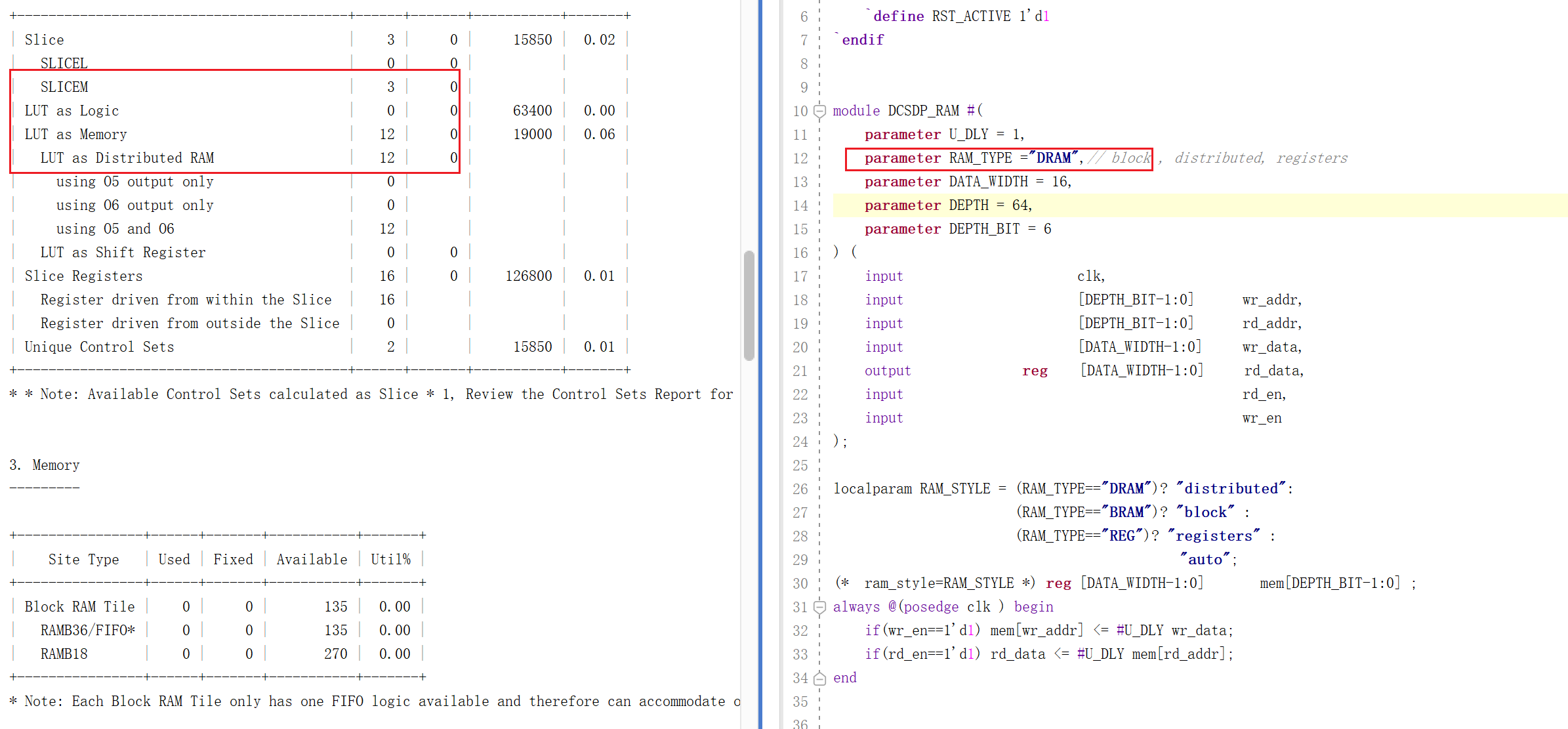

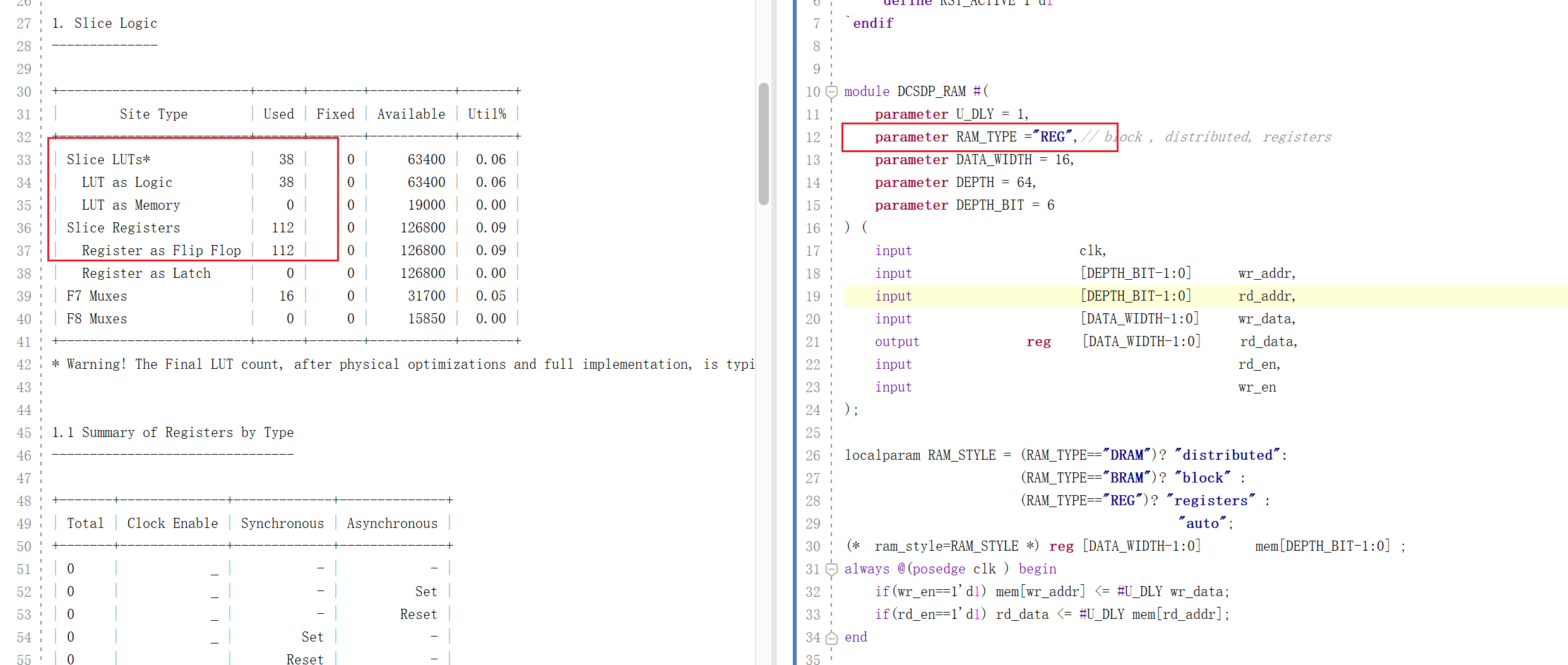

以下为资源占用情况:

BRAM

DRAM

REG

参考资料:

https://blog.csdn.net/weiaipan1314/article/details/104327009

https://blog.csdn.net/weiaipan1314/article/details/104328475

https://fpga.eetrend.com/files-eetrend-xilinx/download/201408/7595-13762-ug4747seriesclb.pdf

Verilog 实现不同类型的RAM

https://blog.songshiyu.cn/archives/verilog-shi-xian-bu-tong-lei-xing-de-ram

评论