本系列文章为《High Speed Serdes Devices and Applications》的学习总结,素材主要取自教材,并附带一些自己的思考。原书下载链接:High Speed Serdes Devices and Applications.pdf.

时钟恢复(Clock Data Recovery,简称CDR)是一种在数字通信系统中用于从接收到的数据流中提取并重建时钟信号的技术。CDR主要应用于有线通信,用于高速数据传输时恢复时钟,可以减小jtter和噪声(相对于随路时钟),是Serdes中的关键组成部分,通常和DFE联合设计。

从输入串行数据中把clock提取出来

重新确定采样时间,正确采样数据(找到眼图中心)

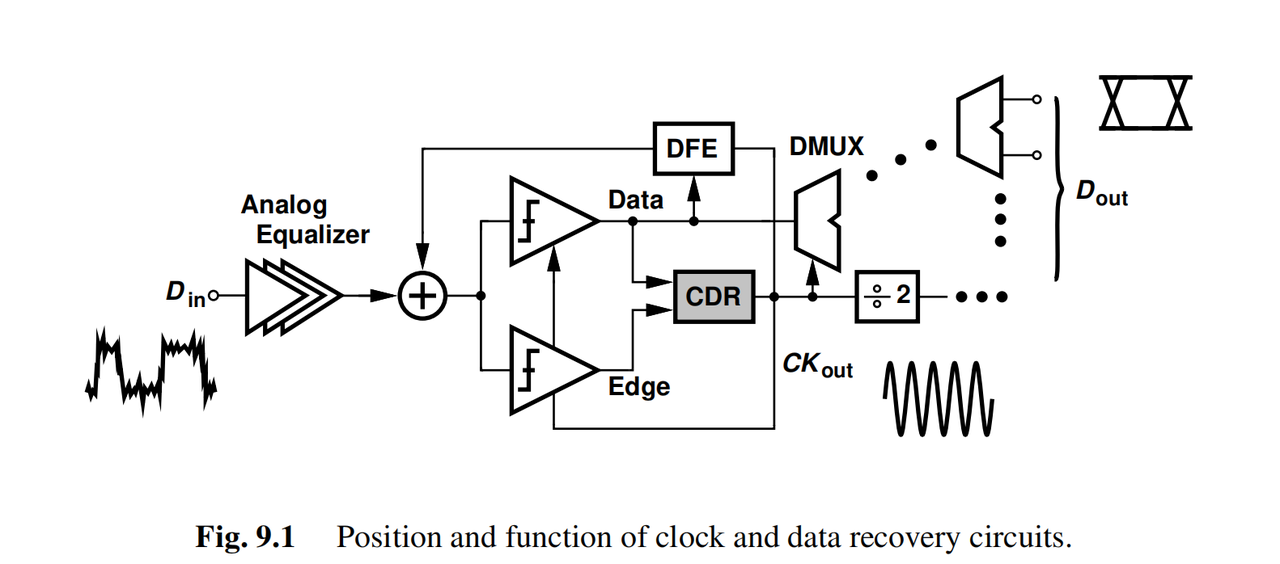

CDR在Serdes中的位置如上图所示,数据进入之后采样并提取跳变沿一起送入CDR模块,恢复出时钟CK_out,通过环路重新对Data进行采样,采样后的数据送给DFE均衡。图中的Data就已经是重新采样过后的数据,然后再逐步靠分频时钟进行串并转换。

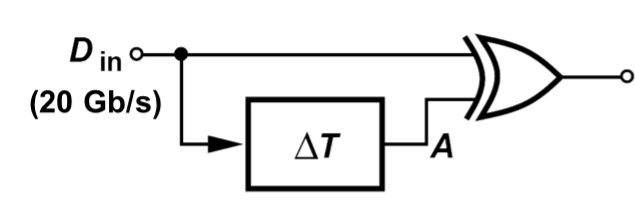

设计CDR的思路就是如何提取数据的跳变沿,强化数据边沿。通过延迟做边沿检测,可以将每个边沿都检测出来,如下图所示:

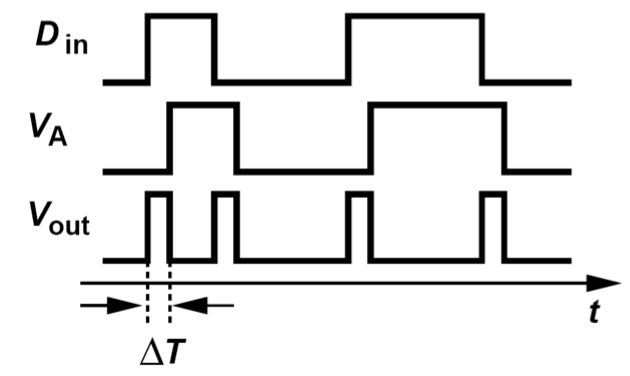

那么就有如下的波形:

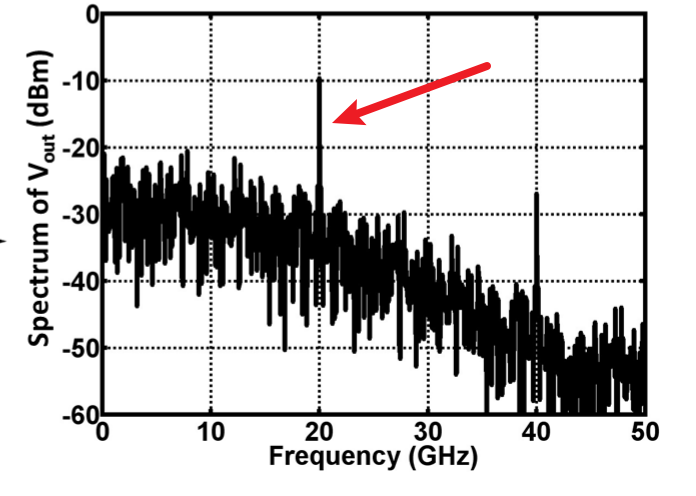

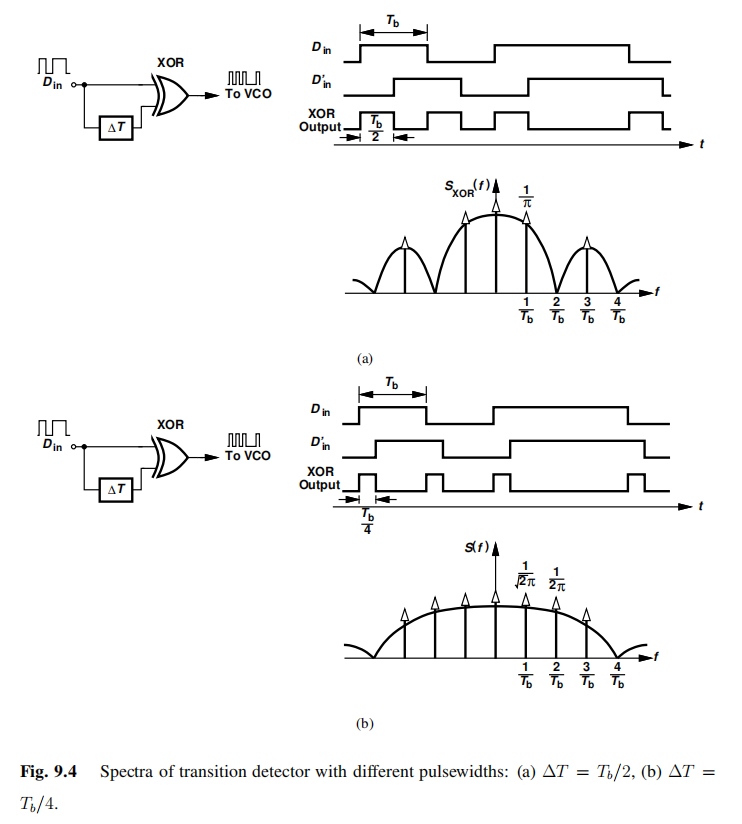

输出信号的频谱图案和delta T有关,脉冲越窄,频谱越宽,但是尖峰的位置不会改变,即恢复时钟的频率:

设置不同大小的T,输出的频谱如下图所示:

如果直接把图中异或得到的输出作为恢复时钟有以下问题:

clock并不是周期性的,应用有限制。因为输出只会在数据跳变变沿才有脉冲。

当Data rate很快,基本上无法产生一个矩形波,输出电压还没来得及稳定就开始降低了。

这种方式没有做到用恢复时钟重新去采样输入数据。

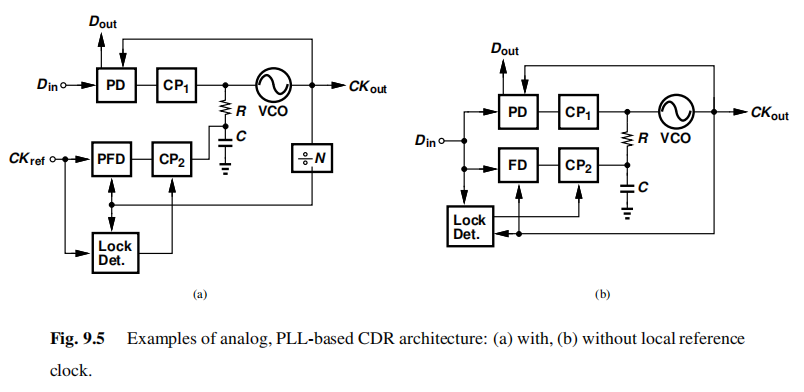

因此,CDR还需要一个PLL来锁定输出的clock,以保证输入数据和恢复时钟之间的相位关系,让恢复时钟上升沿处于眼图的中间。参考之前讲的PFD-based PLL,找到一个理想的PFD就可以通过环路锁定恢复时钟了,但是事实上没有这样的PFD,因为与PLL中的周期时钟不同,这里的输入Data不是周期的,无法锁定。那么可以将锁定过程分为两部分,一个PD和一个FD,先通过FD大致锁定频率,再用PD微调锁定相位即可。

如图9-5所展示的两种PLL-based CDR结构,主要区别在于左图需要参考时钟输入,下半部分为一个完整的PLL结构;右图不需要参考时钟,直接将输入数据和恢复时钟进行比较控制VCO的输出。图中的LockDec模块是为了在锁定状态下关闭FD,即如果频率大致锁定上了,就不需要FD/PFD工作了,既有利于系统稳定,又能降低功耗。

参考链接:李致毅教授 B 站视频:鳌中堂讲电路

Serdes 学习笔记,CDR时钟恢复(其一,基本 CDR原理和结构)

https://blog.songshiyu.cn/archives/serdes-xue-xi-bi-ji-cdrshi-zhong-hui-fu-qi-yi-primitive-cdr

评论