本文最后更新于2025-04-04,距今已有 383 天,若文章内容或图片链接失效,请留言反馈。

个人笔记,没有参考价值~

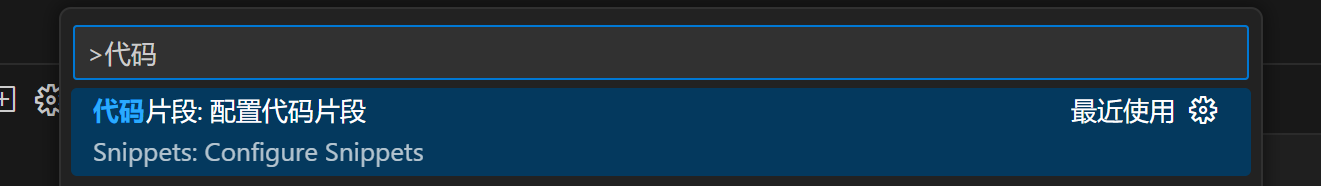

输入ctrl+shift+P,输入代码,选择插入代码片段。

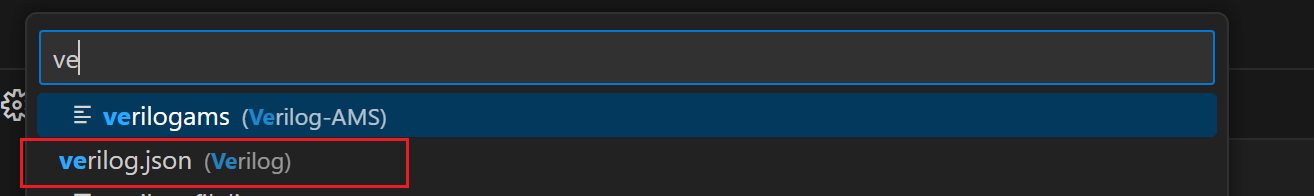

选择verilog:

编辑json文件,以下为参考代码,可以根据自己需要修改:

编辑json文件,以下为参考代码,可以根据自己需要修改:

{

"Verilog Module with Clock and Configurable Reset (Postedge Default)": {

"prefix": "newmodule",

"body": [

"`ifdef RST_ACTIVE_LOW",

" `define RST_Edge negedge",

" `define RST_ACTIVE 1'd0",

"`else",

" `define RST_Edge posedge",

" `define RST_ACTIVE 1'd1",

"`endif",

"",

"",

"module ${1:module_name} #(",

" parameter U_DLY = 1",

") (",

" input clk,",

" input rst,",

"",

" output ${2:output_signal},",

" input ${3:input_signal}",

");",

" ",

" wire ${4:internal_signal};",

"",

" always @(posedge clk or `RST_Edge rst) begin",

" if (rst == RST_ACTIVE) begin ",

" ${5:reset_state} <= #U_DLY ${6:initial_value};",

" end else begin",

" ${7:next_state} <= #U_DLY ${8:next_value};",

" end",

" end",

"",

"",

"endmodule"

],

"description": "Generates a Verilog module with clock, configurable reset polarity (default active-high/posedge), and basic structure."

},

"Always Posedge Clock with Reset": {

"prefix": "always_rst", // 你可以根据喜好修改触发词

"body": [

"always @(posedge clk or `RST_Edge rst) begin",

"\tif (rst == RST_ACTIVE}) begin ",

"",

"\tend else begin",

"",

"\tend",

"end"

],

"description": "Generate always @(posedge clk or RST_Edge rst) block"

}

}此时,输入newmodule 按tab键会自动生成片段1,输入always_rst可以自动生成片段2。

VSCode 配置Verilog 代码片段联想

https://blog.songshiyu.cn/archives/vscode-pei-zhi-verilog-dai-ma-pian-duan-lian-xiang

评论