前言:本文属于历史项目,跨越的时间线非常长,从 2021 到 2024 年,主要涉及的版本有 MATLAB 2022a 和 MATLAB 2024a。有部分函数和代码都是继承的 2022a,现在我整理时用的 2024a,会发现 HDL Coder 工具箱在这两年变化挺大,新增了很多功能,手册也修改了很多。如果文中的描述不准确,请自行查阅官方文档。

1. HDL Coder开发流程

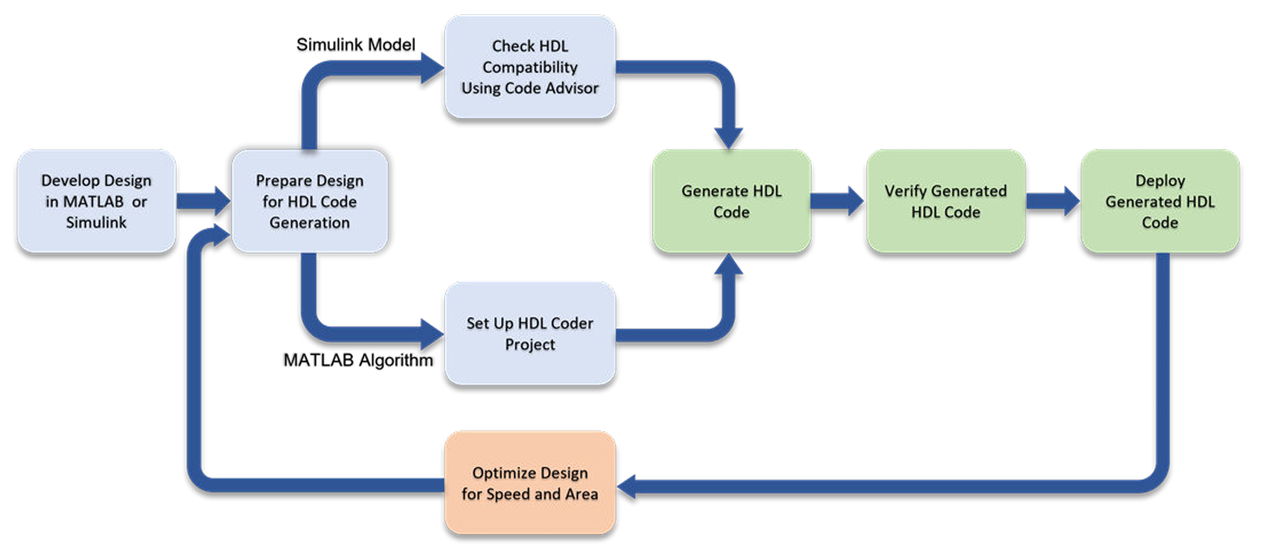

上图展示了使用 HDL Coder 工具箱生成和优化 HDL 代码的工作流程,具体可以分为以下几步:

Develop Algorithm in Simulink or MATLAB(在 Simulink 或 MATLAB 中开发算法):

开发者可以在 Simulink 或 MATLAB 环境中设计算法。为了确保代码兼容 HDL 生成,编写 MATLAB 算法时要使用符合 HDL 语法和功能的函数。对于 Simulink 设计,应使用 HDL 兼容的 Simulink 模块。

Prepare Design for HDL Code Generation(准备HDL 代码生成):

将设计准备好,以便进行 HDL 代码生成,可能包括debug调试等。

Check HDL Compatibility Using Code Advisor(使用 Code Advisor 检查 HDL生成的 兼容性):

使用 Code Advisor 检查设计是否兼容 HDL 代码生成。Code Advisor 会给出兼容性建议和可能的改进点,以确保模型可以生成高效的 HDL 代码。

Set Up HDL Coder Project(设置 HDL Coder 项目):

建立 HDL Coder 项目,用于管理代码生成过程中的各项参数和设置。包含目标硬件选型、优化选项等信息。

Generate HDL Code(生成 HDL 代码):

运行 HDL Coder 工具生成 HDL 代码。此代码可以直接用于 FPGA 或 ASIC 的设计实现。

Optimize Design for Speed and Area(优化设计以提高速度和面积效率):

优化生成的 HDL 代码,以提高执行速度或降低面积需求。这一过程可能包括资源共享、流水线等分别用于面积优化和时序优化。

Verify Generated Code(验证生成的代码):

验证生成的 HDL 代码,以确保它的功能和性能符合预期。包括仿真测试和后端,以确保代码在实际硬件上的运行效果。

Deploy Generated Code(部署生成的代码):

最终将验证通过的 HDL 代码部署到硬件设备上,如 FPGA 或 ASIC,完成设计的硬件实现。

2. 使用Simulink生成HDL 代码

1) 新建空白文件

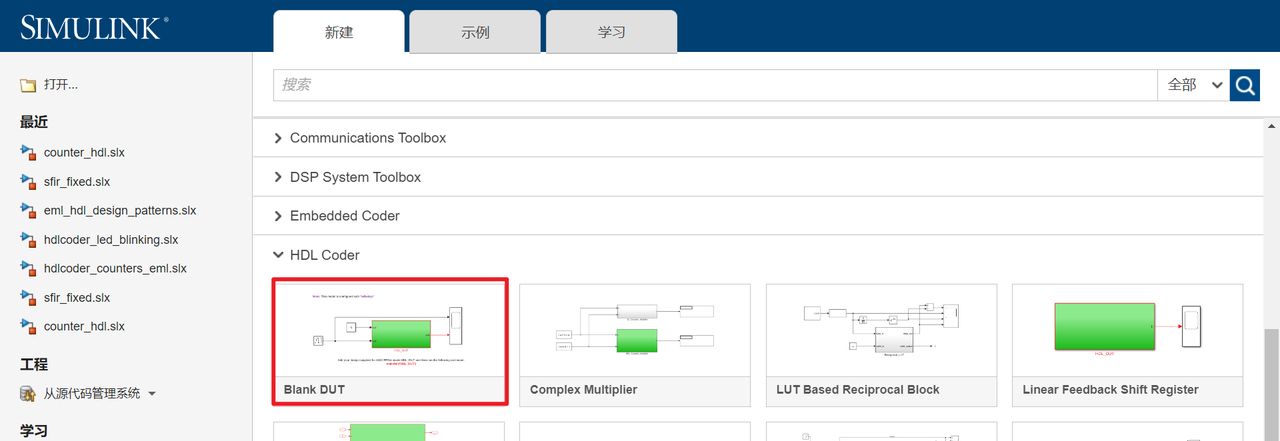

在MATLAB主界面启动Simulink,选择HDL Coder下的 Blank DUT。

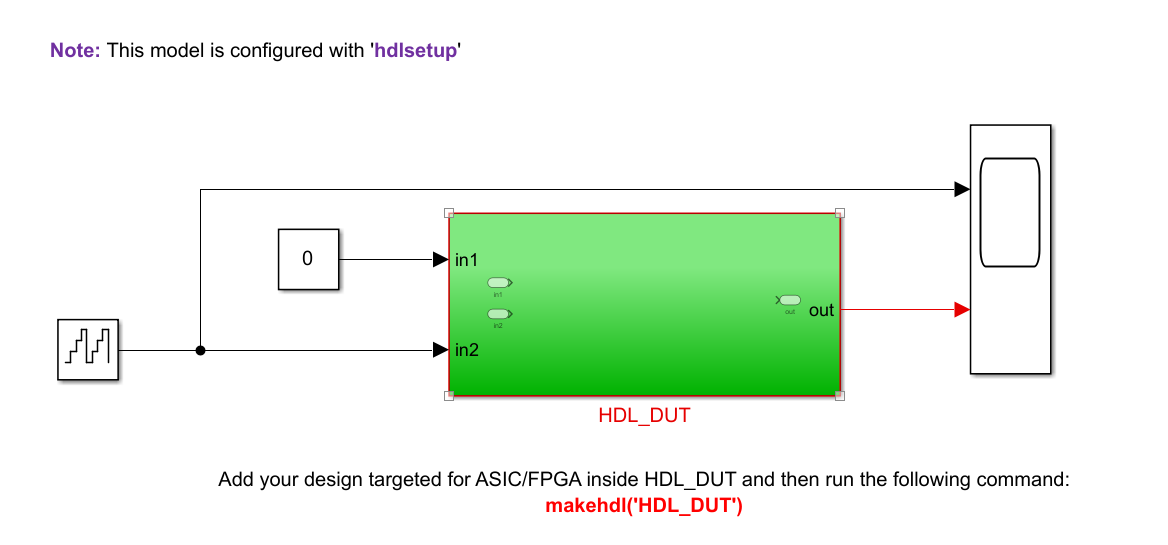

得到以下文件:

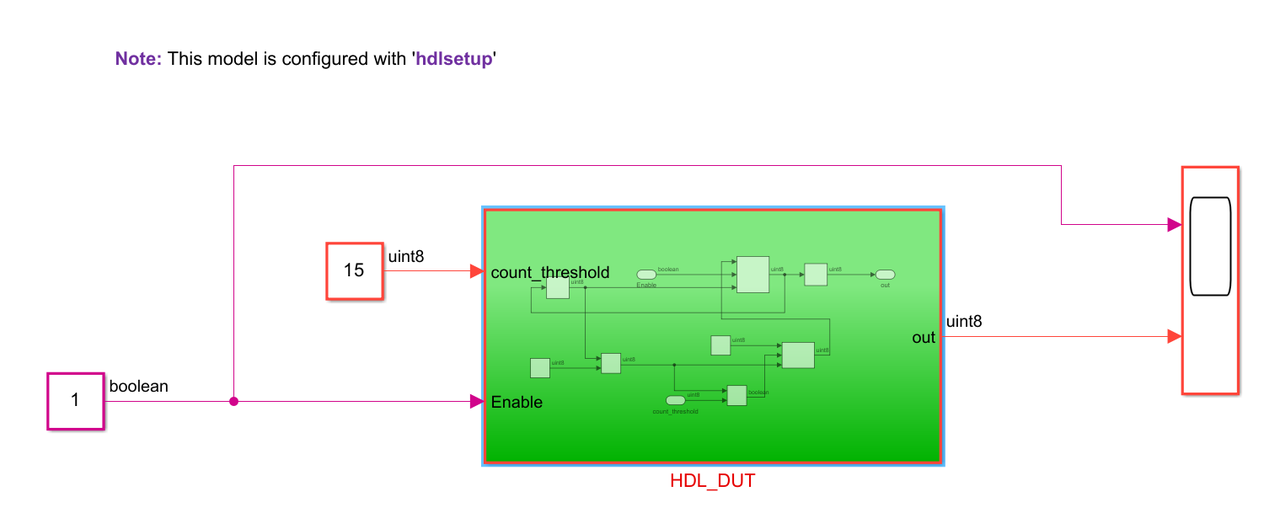

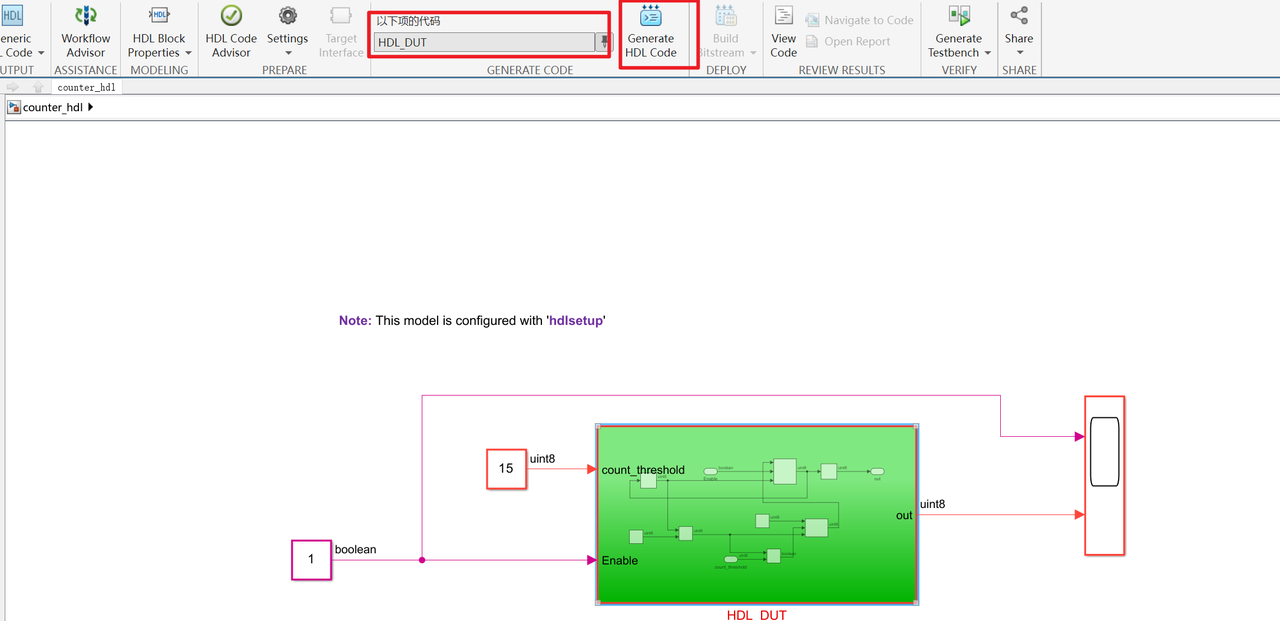

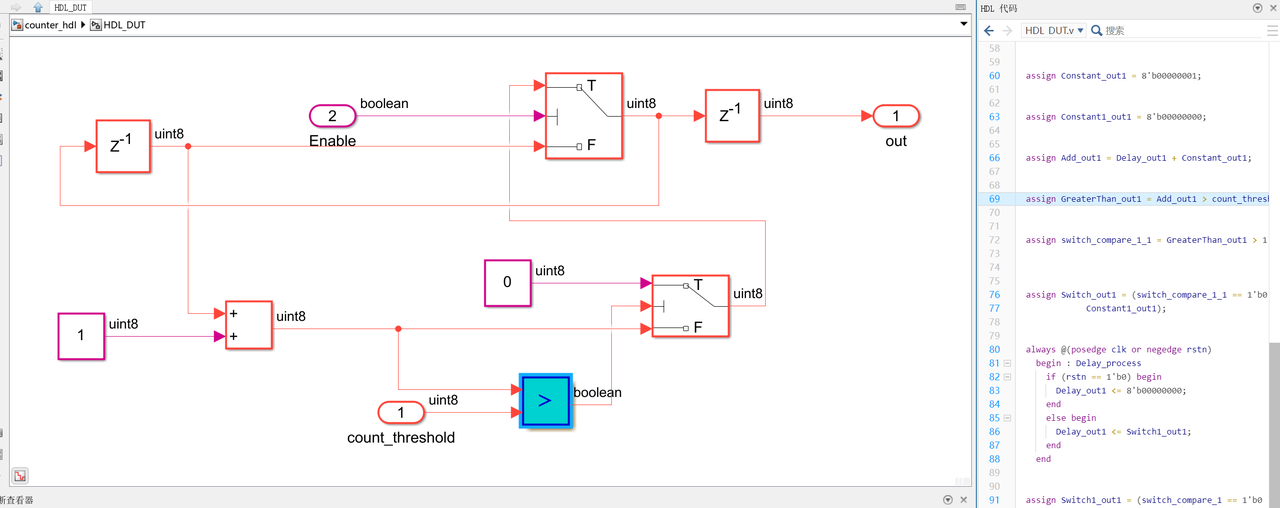

搭建如图所示的一个计数器模型:

需要注意每个模块的数据类型。

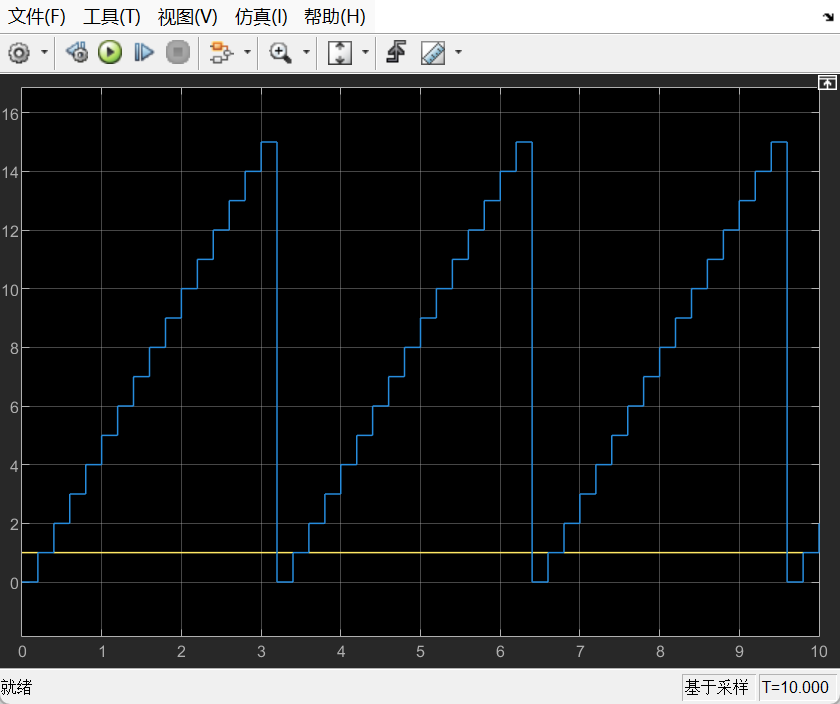

这个模型实现了一个计数器的功能,HDL_DUT的输入端口 count_threshold 是计数器的计数最大值,点击运行可以查看仿真波形。

2) 生成 HDL 代码

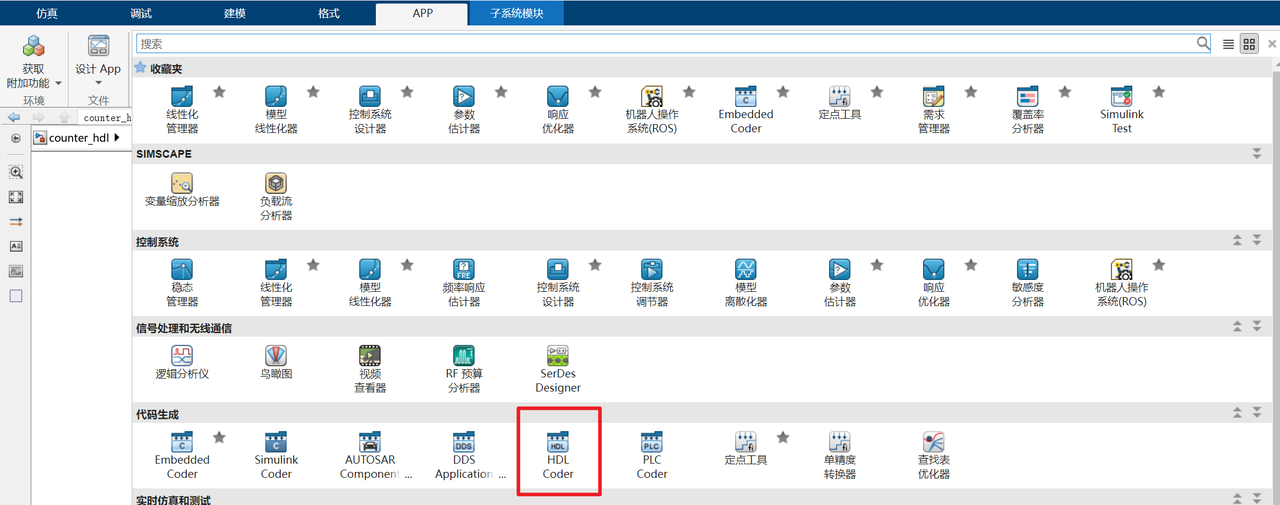

在顶端选项中选择APP,找到HDL Coder。

点击后会在窗口新建标签,在HDL Coder Setting中对代码生成的参数进行设置。

常用的有:

HDL Coder Generation-> Set Basic Options -> Language -> Verilog

Global Settings 自行设置

Report-> Generate traceability report -> Line Level

其他设置读者自行摸索。

选中HDL_DUT 模块,点击 Generate HDL Coder,需要确保左框中显示的是正确的层级。

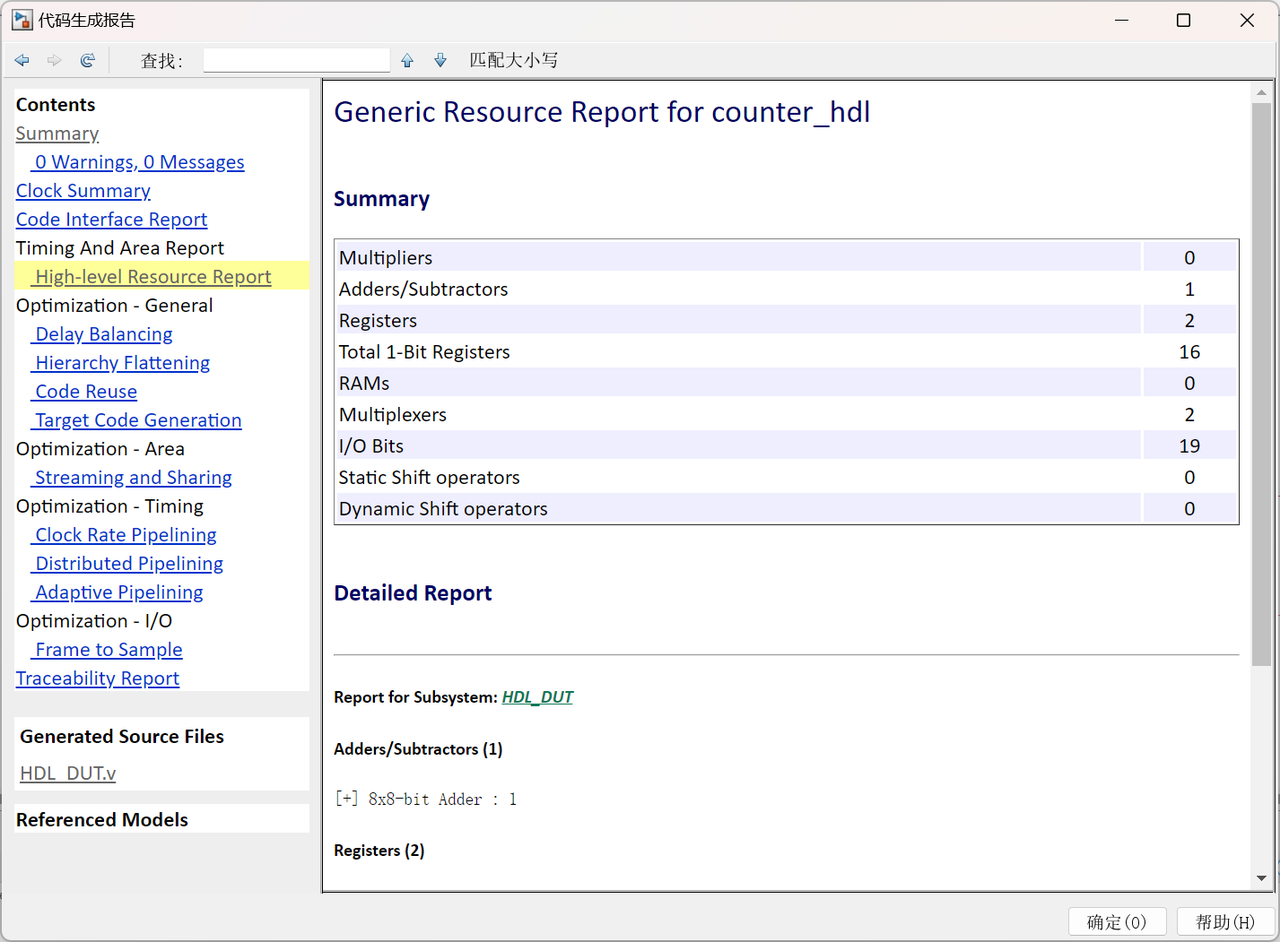

运行后能够查看到运行报告:

进入DUT 内部可以双向跟踪代码和模块的对应关系:

单击模块可以高亮对应的代码,单击代码的行号可以高亮对应的模块。

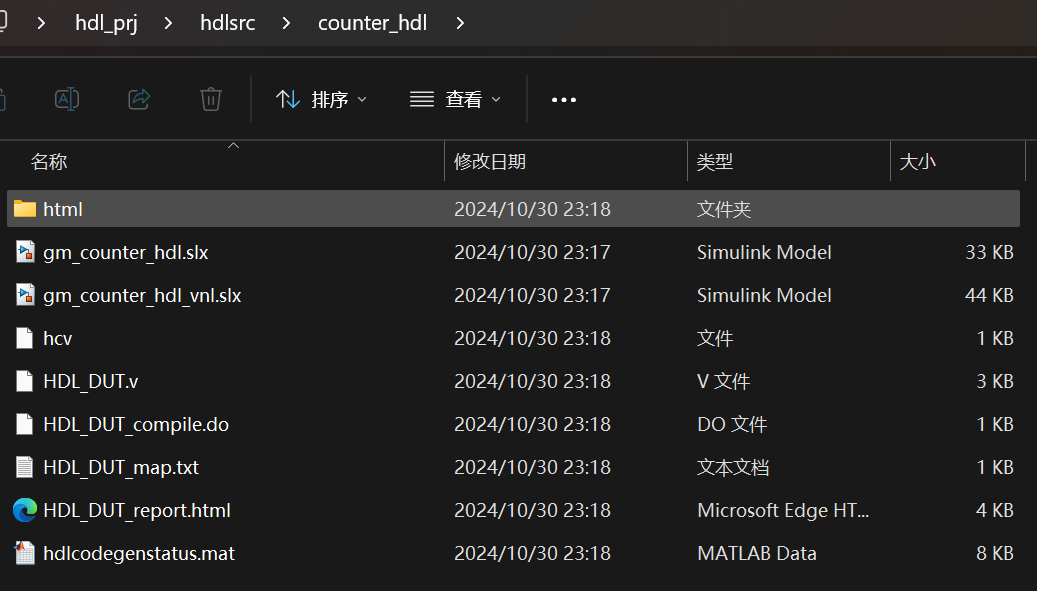

3) hdlsrc文件夹内容说明

hdlsrc 文件夹

当 HDL Coder 完成代码生成后,会在当前文件夹下创建一个名为

hdlsrc的文件夹。双击进入

hdlsrc文件夹,找到与模型名称相同的子文件夹,里面存放了生成的 HDL 代码和相关文件。

HDL 代码文件

HDL_DUT.v:这是生成的 Verilog 代码文件,包含模型中设计的主要逻辑模块(例如,一个计数器)的实体定义和 RTL 架构。

HDL_DUT_compile.do:Siemens ModelSim 编译脚本

这是一个 ModelSim 的编译脚本(.do 文件),用于将生成的 HDL 代码导入 ModelSim 中进行编译和仿真。

HDL_DUT_map.txt:映射文件

映射文件用于将生成的 HDL 代码中的实体或模块与原始 Simulink 模型中的子系统对应起来。

HDL_DUT_report.html:HDL 检查报告

这是一个 HTML 格式的报告文件,包含代码生成过程中的状态、警告和消息。

gm_hdlcoder_simple_up_counter.slx:生成的行为模型

这是生成的 Simulink 模型文件(文件名前缀为

gm_),它行为上等效于 HDL 代码。该模型是位真(bit-true)的,这意味着其模拟输出与生成的 HDL 代码的行为完全一致,用于在 Simulink 中验证 HDL 代码。

hcv 文件:HDL 代码查看文件

hcv文件用于在 Simulink 的 Code View 面板中显示生成的 HDL 代码。在 HDL Coder 应用程序中点击 View Code 按钮,即可通过此文件在 Simulink 中查看 HDL 代码。

在生成的代码中,无需考虑时钟和复位信号,这些信号在前文中的HDL Coder Setting中设置,可以修改端口名,同步/异步复位,高低电平有效,上升沿/下降沿触发等等。当模型中包含时序逻辑时,这些信号都会自动生成,但当模型完全为组合逻辑时,这些信号不会生成(除非手动指定)。

3. 使用MATLAB 函数生成HDL 代码

待补充~

MATLAB HDL Coder 开发入门

https://blog.songshiyu.cn/archives/matlab-hdl-coder-kai-fa-ru-men

评论