本系列文章为《High Speed Serdes Devices and Applications》的学习总结,素材取自教材,并附带一些自己的思考。原书下载链接:High Speed Serdes Devices and Applications.pdf

SERDES,全称 Serializer/Deserializer(串行器/解串器),是一种用于高速度点对点(P2P)串行通信的技术。它通过时分多路复用(TDM)将发送端的多条低速并行信号转换为一条高速串行信号,经过传输介质(如光缆或铜线)传输后,在接收端将高速串行信号重新转换为低速并行信号。

SERDES 的主要技术优点包括:

减少 I/O 引脚和连接:通过串行传输,显著降低芯片所需的引脚数量,简化硬件设计并降低成本。

提高数据传输速度:串行传输支持更高频率,克服了并行传输在高速度下的时钟偏移和串扰问题。

改善信号完整性:减少电磁干扰(EMI)和串扰,确保长距离传输的信号质量。

降低功耗:相比并行接口,串行接口在高速度下消耗更少功率。

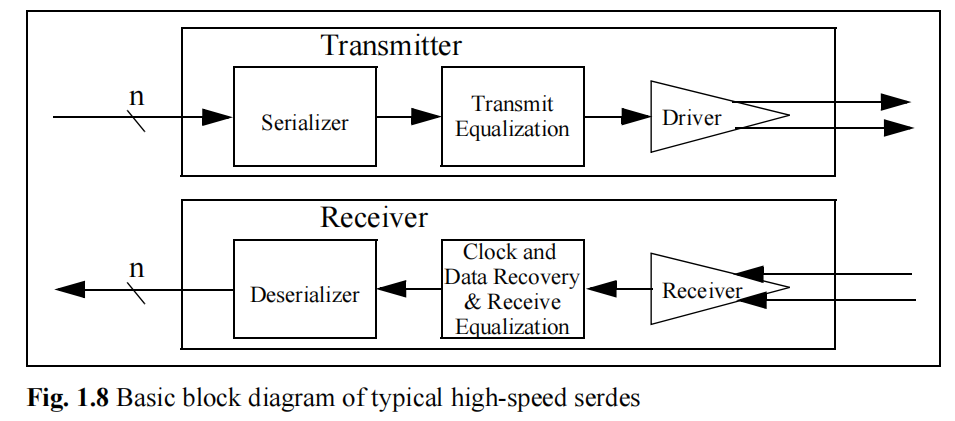

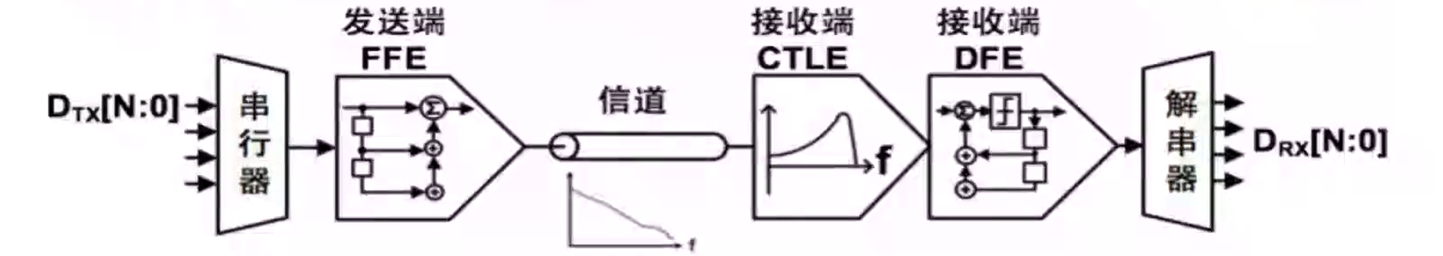

一个简化的serdes内部结构图可以参考图1.8,并行数据经过串行化后在发送端均衡后通过差分信号发送出去,这里不包含时钟。接收端会从接收数据中恢复出时钟(CDR),并再次均衡后串并转换得到原始数据。恢复出的时钟要求与数据对齐,这样可以得到每个bit位的最佳采样点,降低误码率。

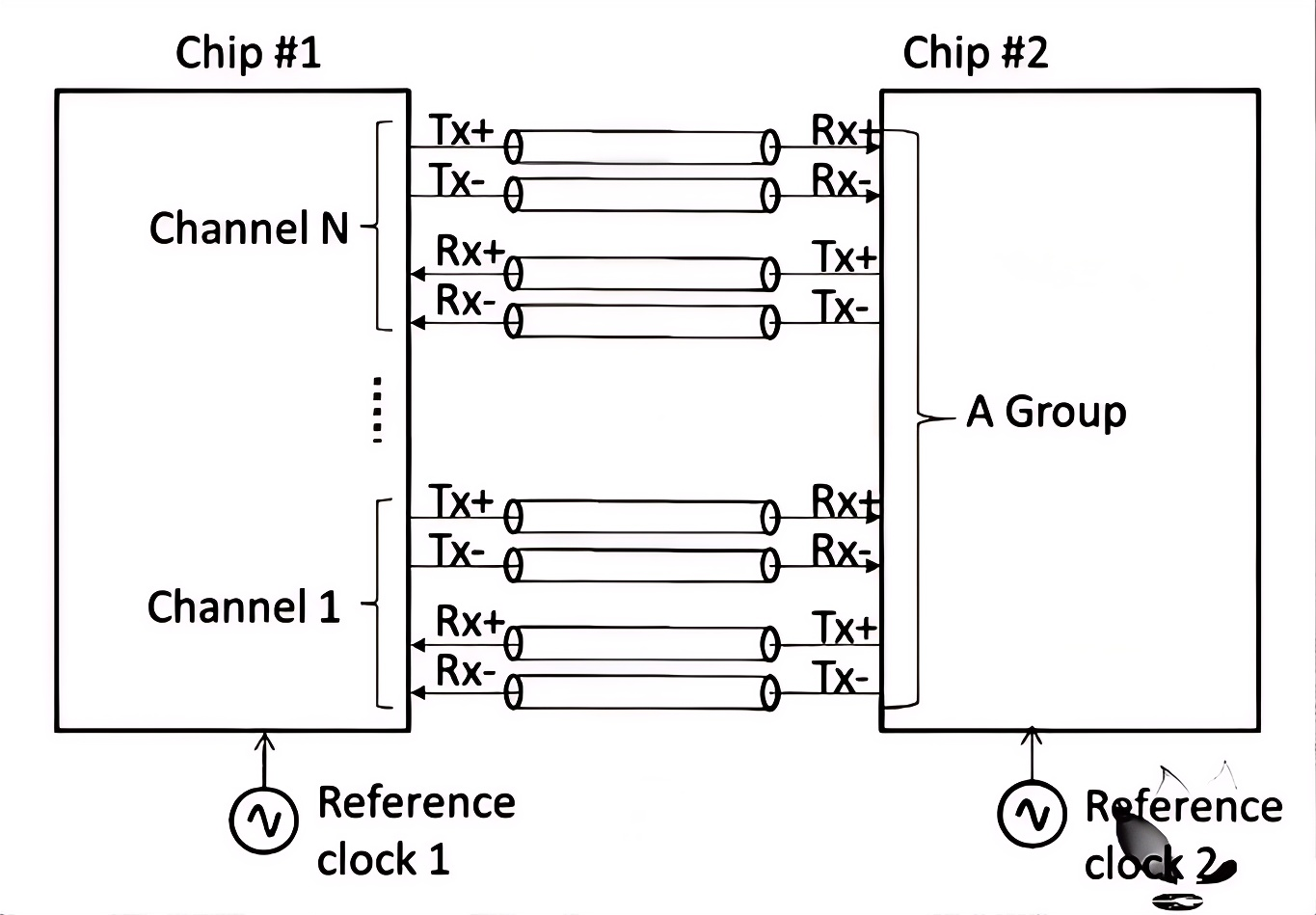

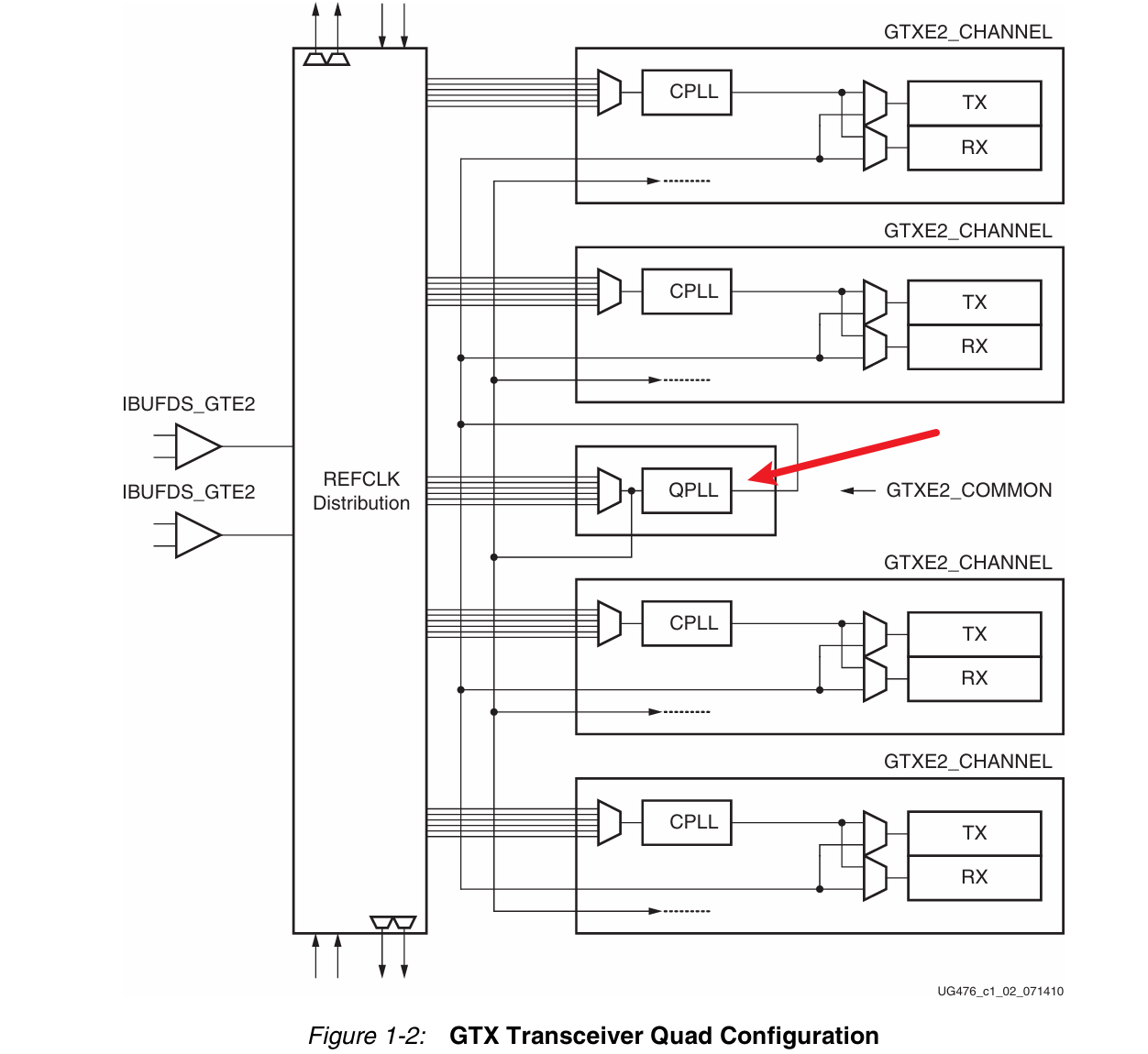

通常会将多路serdes信号集成在一个设备上如上图所示,虽然每一路的serdes的工作流程是完全独立的,但是这种方式可以让多路serdes 共享部分电路,例如PLL,以获得更优的面积功耗和成本。例如下图为Xilinx FPGA中的serdes结构图,在同一个 Quad内,不同channel可以共享同一个QPLL,他们也可以使用各自独立的CPLL。

串行/解串模块

Serdes 的输入数据为并行数据,通常位宽通常是8bit或者10bit的倍数,8bit的话就是没有经过8b10b编码的数据,10bit是已经经过8b10b的数据,区别在于8bit输入可以选择8b10b在serdes中完成。

串行化数据不一定是单次完成了,在给均衡器(Equalization)之前的数据并非一定是单bit位宽,比如可以是先将8bit转换成2bit位宽,剩下的2bit转单bit由均衡器完成。这样做的好处在于可以使均衡器工作在较低的时钟下,单bit的串行均衡比2bit的并行均衡器工作时钟快2倍。

解串模块完成了串行模块相反的工作,它将接收到的高速串行信号恢复成多bit的并行信号。串行数据的采样信号是通过串行数据自身恢复出来的,并行时钟是由外部输入的参考时钟经过PLL倍频得到的,与采样时钟之间有倍数差,这个并行时钟可以给serdes外部逻辑使用。

许多解串模块还会包含对齐功能,因为在串并转换的过程中,不可能直接精准恢复到原来的一个一个字节,可能存在bit位的偏移,例如将上一个字节的末尾的bit位放在了下一个字节的最前面,整体有1bit的偏移,这样串并转换出来的所有数据都是错误的。因此还需要通过串行数据的滑动,恢复出正确的位序。

均衡器

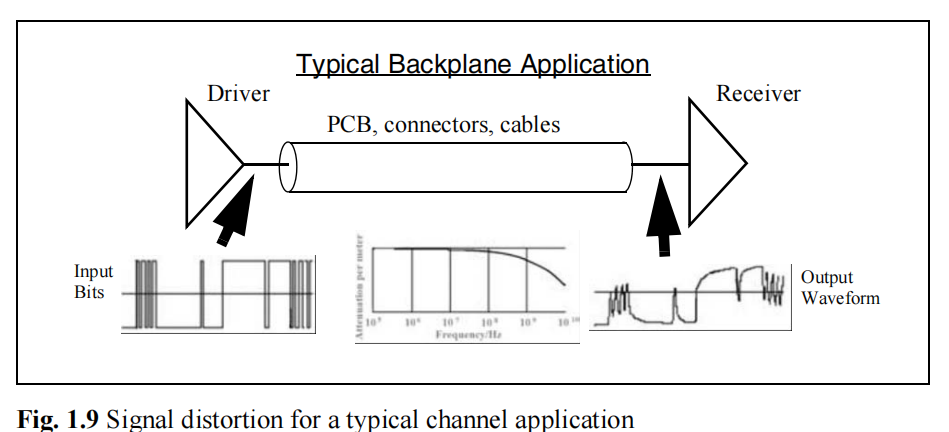

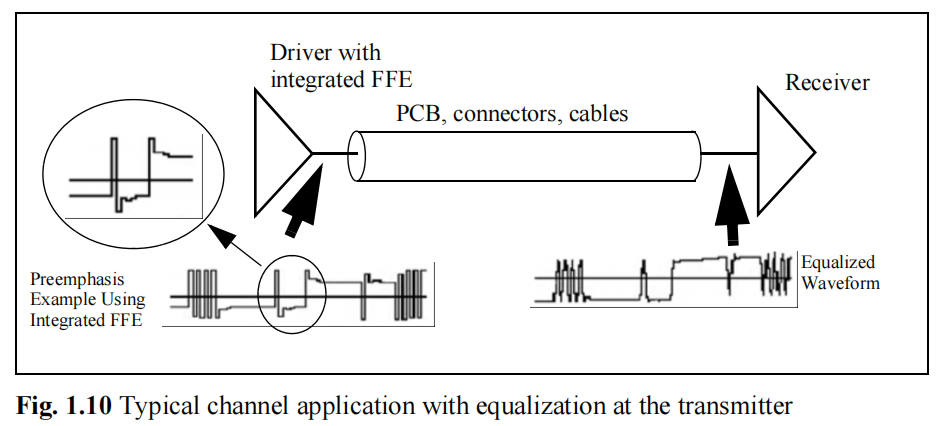

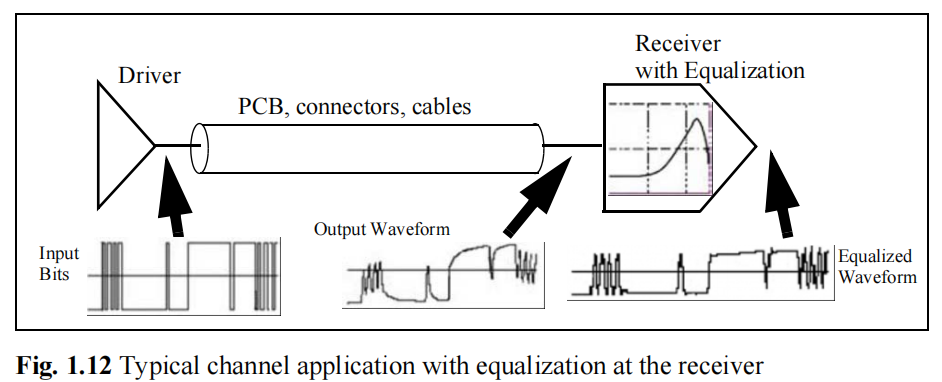

发送端和接收端之间的传输路径可以看成一个低通信道,这是由于多种因素造成的,例如导线的趋肤效应,寄生电容,高频串扰等等。一个典型的背板传输波形如图1.9所示。

即使发送的是一个完美的矩形波,接收到的波形也会在边沿处变缓,整体的信道频率响应见中间的滤波器频率响应。频率越高,增益越低。因此我们可以在发送数据之前做预加重,即让数据先通过一个与信道传递函数相反的滤波器,那么整体的传递函数就是 H =1,为理想信道。该处理在时域上的表现就是信号在跳变处的能量更大,类似于过冲,如下图所示。

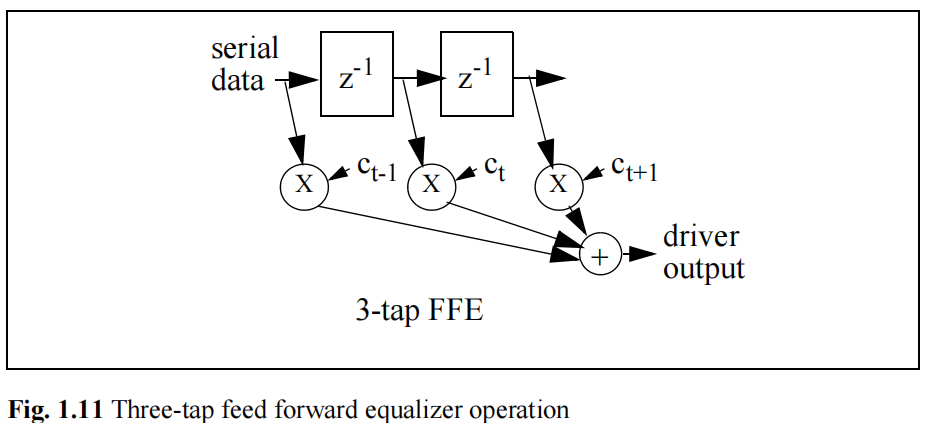

因此大多数serdes在发送前会经过FFE(前馈均衡,Feed-Forward Equalization),其实就是一个FIR滤波器。通过对输入信号进行加权和延迟处理,增强高频分量或抑制低频分量,以抵消信道引起的频率选择性衰减。其核心思想是利用一组可调的抽头(Tap)系数,对信号的不同延迟版本进行加权求和,从而重塑信号波形,使其在接收端更接近原始信号。其结构如图所示,抽头之间的delay是一个码元周期。

前向抽头(Pre-cursor Taps)用于补偿信道的非因果部分。k<0

后向抽头(Post-cursor Taps)用于补偿信道的因果部分。k>0

这里的系数除了k=0为正数,其他值都是负数,都是减去其他码元对当前码元的干扰。

至于FFE滤波器的每个抽头系数的值怎么选择,以及对应的自适应算法应该每个厂商都是有自己的设计。

除了在发送端做均衡以外,还需要在接收端做均衡,发送端的处理相当于是缓解一下接收端的压力,同时还可以提高信噪比。接收端的均衡手段包括CTLE、DFE等,CTLE可以看成一个模拟的高通滤波器,或者说是一个高频放大器,重点是它是纯模拟的,因此没有采样过程,是连续时间的。CTLE会放大高频噪声,因为它是直接把接收信号的高频部分放大,会放大信号的同时放大噪声。

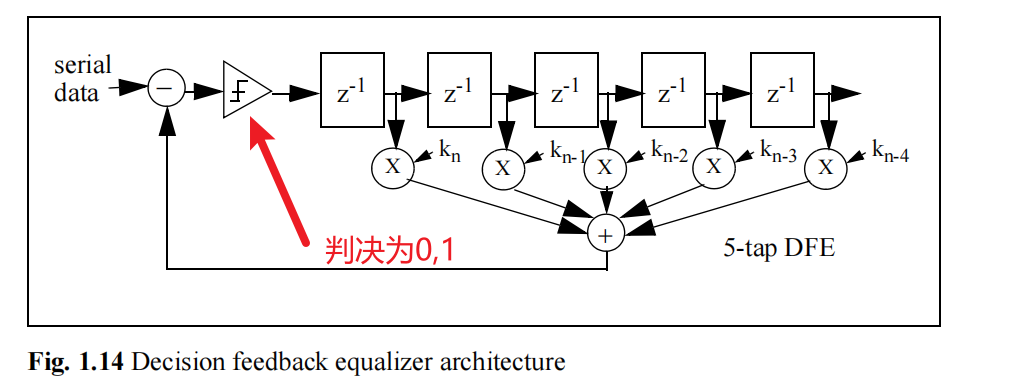

DFE为判决反馈均衡器,这是一个非线性的均衡器,它的主要结构也是一个滤波器,只是它是先判决0,1之后将判决后的数据作为反馈输入滤波器。

注意DFE是没有前向抽头(Pre-cursor Taps)的,只能解决信号拖尾造成的ISI,同时它并不会放大高频噪声,因为它的反馈输入使用的是判决后的数据,即0或者1,可以看作为精确的输入,这也是它非线性均衡的缘由。在判决的时候就消除了噪声,这也是数字信号的一个好处。

我们可以通过下面这个图片来理解DFE,我们发送一个数据之后的接收波形为最左边的冲击信号,明显这个波形会导致接下来的几个采样点的电平不为0,这就是说会影响到之后的几个码元的采样。为了保证其他采样点的电平为0,得到右边的波形图,我们就需要将几个码元的数据叠加,叠加的系数可以通过自适应算法得到。我们不在乎其他时刻的电平误差是否被放大了,只需要关注采样时刻的值。

这个图也反映出DFE是没有前向抽头解决非因果部分的,也就是图中的第一个采样点的非零值无法消除。

通过在接收端的均衡,我们也能在一定程度上恢复出原始信号,如下图:

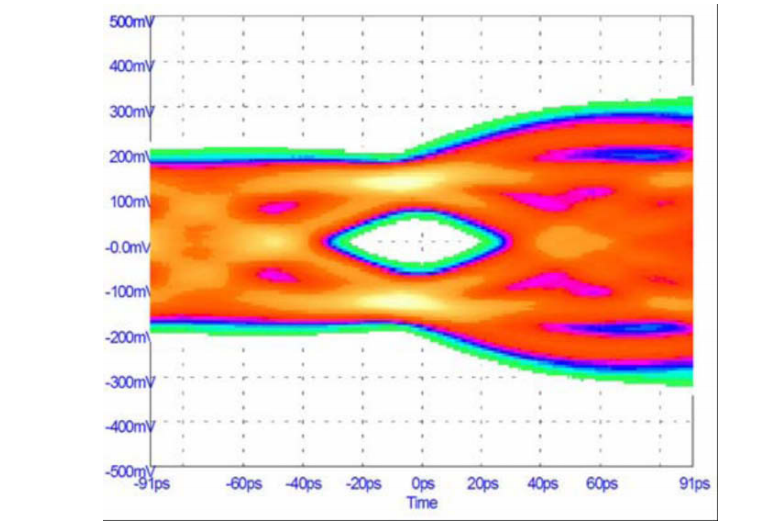

DFE得到的判决结果还可以用于调整采样时间,这个需要和CDR结合,逐bit调整采样点。这一特点可以从下面的眼图看出,经过DFE的眼图虽然是张开了,但是可以发现它仅仅在当前的时刻张开,旁边的眼图并没有张开,这也说明DFE只在乎当前时刻的最佳采样。

CDR(Clock and Data Recovery)

CDR是根据接收数据的跳变,利用接收端的PLL恢复出数据对应的高速时钟,同时还可以找到数据的最佳采样点。在Serdes接收端的CDR恢复出来的时钟并没有直接给其他逻辑或者电路使用,例如串并转换后的并行时钟并非直接从这个恢复出来的高速时钟直接分频得到,而是通过本地的PLL产生。CDR要求数据不能有连续的0或者1,具体的数量根据协议和误码率有不同的要求。因此在发送端通常都需要经过8b10b编码或者加扰,都是为了避免数据长时间不翻转。整个CDR是一个动态的过程,会跟随数据不断调整采样点。

差分驱动器/接收器

差分传输既可以提高信号的抗干扰能力,同时对电压幅度要求降低,例如原来需要1V,现在只需要两个0.5V传输即可,对系统电压的摆幅要求降低,还能降低整体的功耗。

PLL锁相环

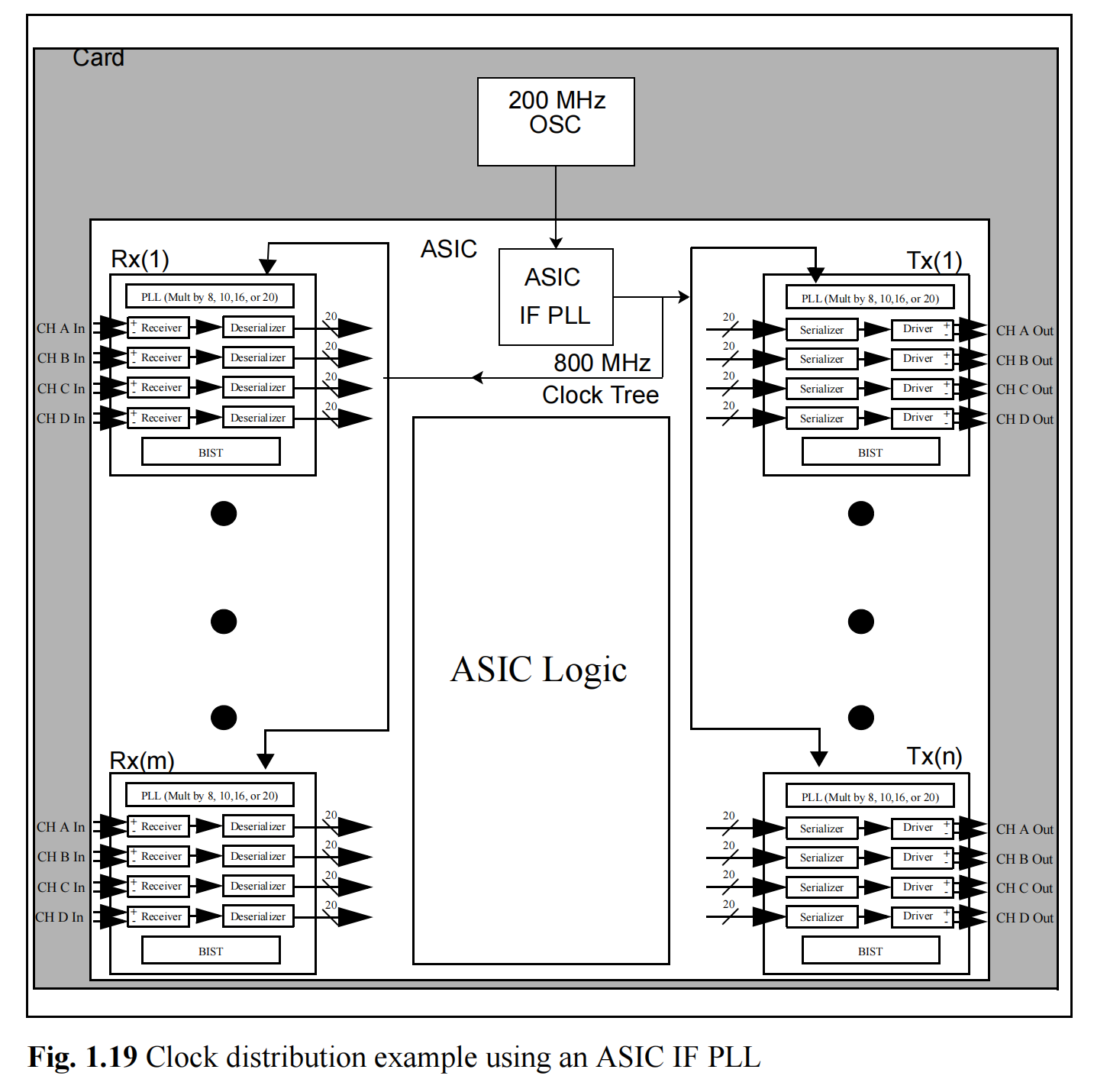

SerDes(Serializer/Deserializer)核心需要一个内部时钟,其运行频率根据驱动器和接收器阶段的架构而定,可以是波特率(baud rate)或半波特率。为了避免在整个芯片内分发高速时钟,通常在芯片内分发一个较低频率的参考时钟,并通过SerDes中的锁相环(PLL)将该时钟频率乘以适当的倍数以达到所需的内部时钟频率。某一SerDes实现可能包含多个发送器和/或接收器通道。在这种情况下,核心内通常使用单个PLL为所有通道生成时钟。

芯片外部的时钟源通常运行在比芯片内部参考时钟更低的频率。为满足所需的芯片内部参考时钟频率,芯片内可能使用额外的PLL来将外部参考时钟的频率进行倍频。由于芯片内部参考时钟的频率通常高于外部参考时钟(但低于SerDes核心的内部时钟),因此产生该时钟的PLL有时被称为中间频率(Intermediate Frequency, IF)PLL。

图1.19展示了一个使用此类IF PLL进行时钟分发的示例。IF PLL将来自芯片外部振荡器的200 MHz时钟频率乘以四,生成800 MHz的参考时钟。该800 MHz参考时钟在芯片内分发至各个SerDes核心。这些SerDes核心各自包含一个PLL,进一步将800 MHz参考时钟的频率提升至所需的波特率。

其他参考文献:

Xilinx GTX手册:ug476_7Series_Transceivers.pdf

Serdes 学习笔记,Serdes结构及原理

https://blog.songshiyu.cn/archives/serdes-xue-xi-bi-ji-serdesjie-gou-ji-yuan-li

评论