本系列文章为《High Speed Serdes Devices and Applications》的学习总结,素材主要取自教材,并附带一些自己的思考。原书下载链接:High Speed Serdes Devices and Applications.pdf。

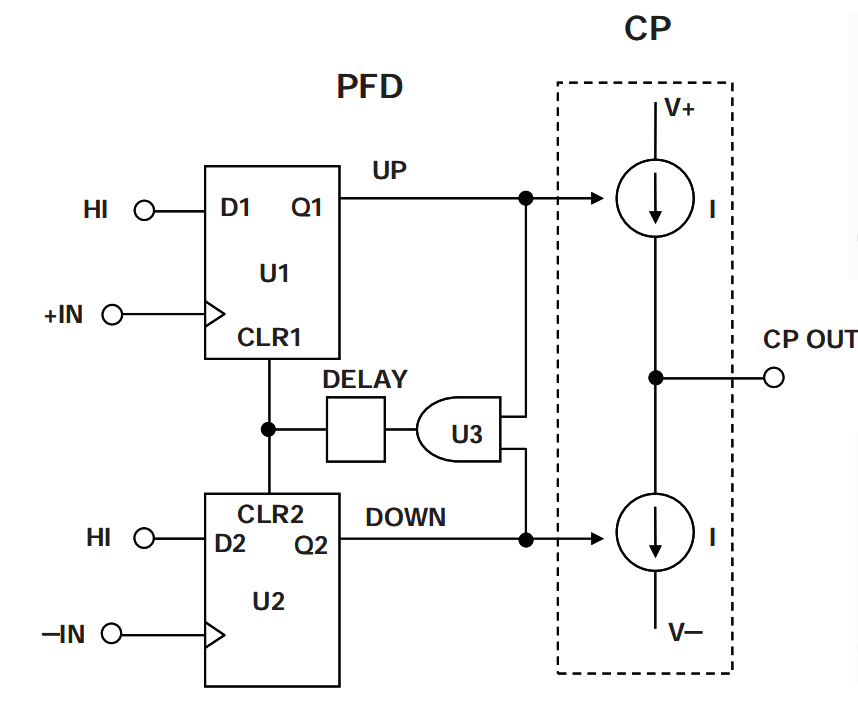

为了克服Simple PLL(Type I)的缺点,提出了改进型的(Type II)PLL,其结构如下所示:

注意到,Simple PLL里面的FD在这里变成了PFD,说明这种类型的PLL不仅可以锁定频率,还可以锁定相位。先忽略这里的DELAY,我们来看一下工作原理。

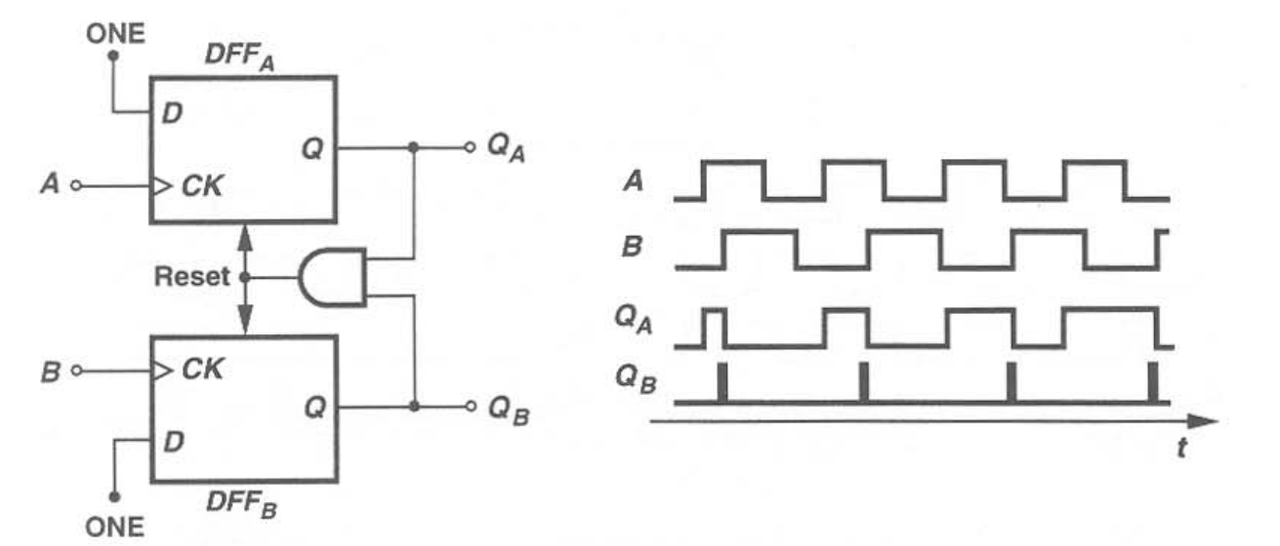

假设两个时钟之间有相位的差别,那么上下两个寄存器的输出可以用上面的图来表示,首先A相位小,QA很快被拉高,然后等待B的上升沿,QB也拉高。此时与门U3被导通,两个寄存器同时复位,输出又再次拉低,其中B的脉冲宽度和整个电路的时延有关,也即电路DELAY。

电路锁定时,QA和QB将会是两个基本一致的窄脉冲,对电容C进行瞬时充放电,保持动态平衡。

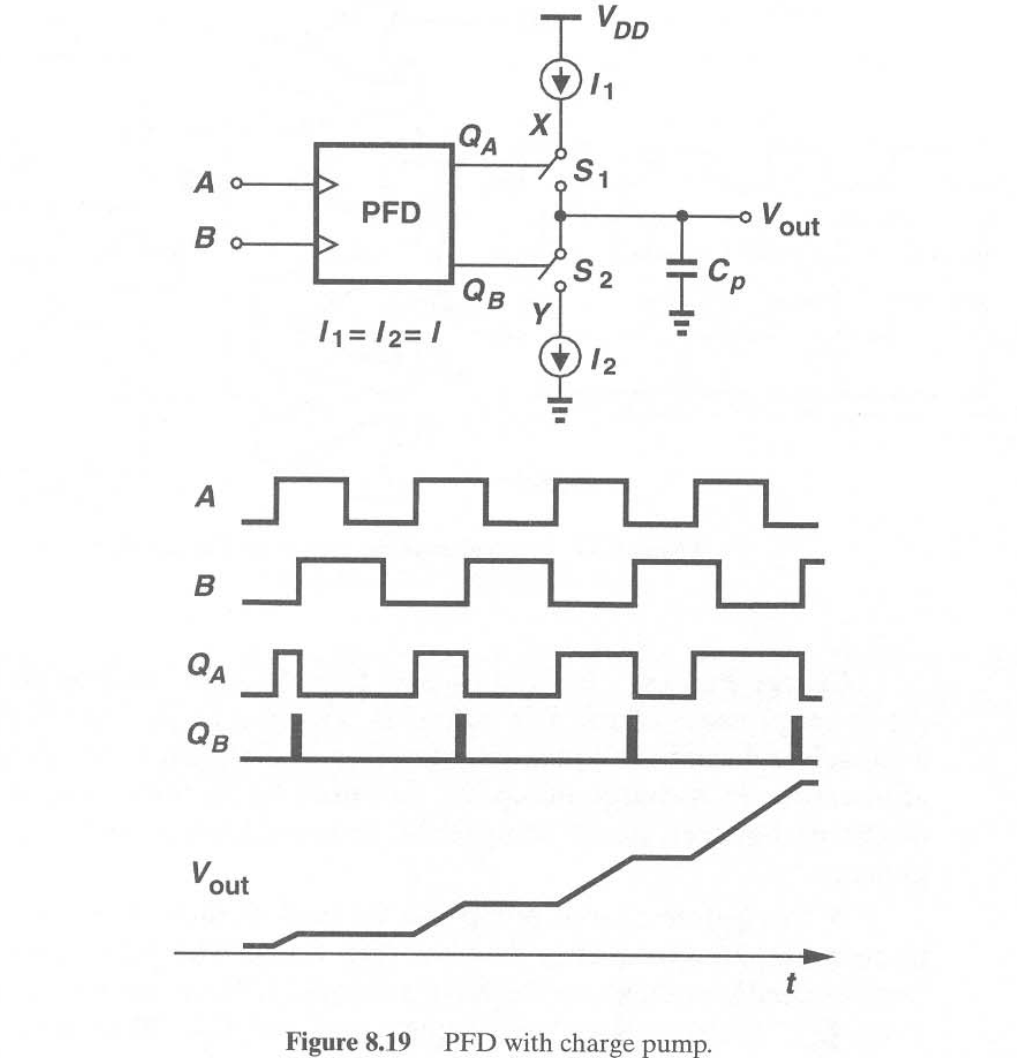

下一步是如何将两个寄存器的输出转换成VCO的电压,这里使用了电荷泵,把寄存器的输出看作是两个开关,控制电流的输入输出,经过电容的转换可以得到对应的控制电压,如下图所示。

从上图也可以看到,输出电压的变化也不是跳变的,相当于通过了一个积分器或者低通滤波器。如果计算上面的闭环传递函数,可以得到:

这里可以看到该函数在虚轴上有两个极点,说明是一个不稳定的系统,存在震荡或者过冲的情况,需要添加一个电阻(消耗型元件)。

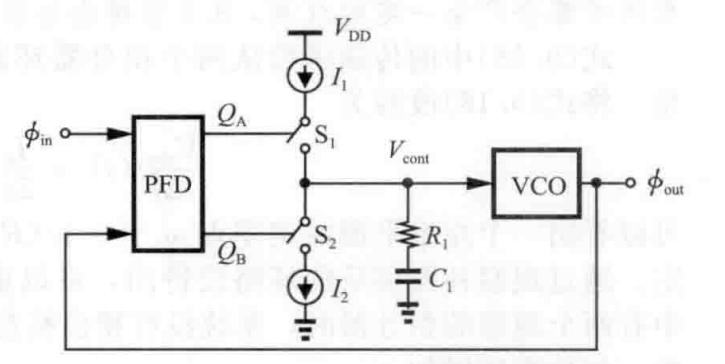

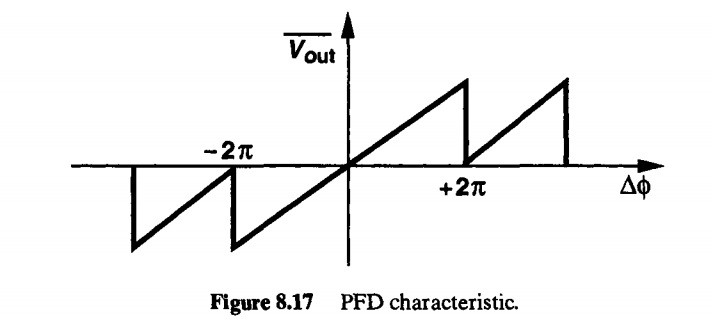

电压和相位差之间的关系,如下图所示:

需要注意的是,相位差在区间表现出单调性,因此在理论情况下一定能锁定到0相位处。相对于前面的Simple PLL,CP PLL可以同时锁定相位和频率。

结果:

相位滞后,VCO电压增大,输出频率变快(频率与相位等价)。

相位超前,VCO电压减小,输出频率变慢。 完成了整个负反馈控制回路。

当然,实际电路不可能这么完美,比如两个电流源的电流不可能完全一致,那么就导致同样脉冲对电压的控制能力不一致,最终会表现为固定的相位差;在锁定时,两个电流源还是会充放电,这里会引入波纹,最终体现在时钟的jitter表现上。该PLL的工作频率还与电路的DELAY紧密相关,如果输入时钟频率过快,开关速度会跟不上,无法锁定。

参考链接:李致毅教授 B 站视频:鳌中堂讲电路

Serdes 学习笔记,锁相环(PLL)结构和原理(其二,CP PLL)

https://blog.songshiyu.cn/archives/serdes-xue-xi-bi-ji-suo-xiang-huan-pll-jie-gou-he-yuan-li-qi-er-cp-pll

评论